# 次世代 SiP(System-in-Package) 自動配線法の検討

A Study of Routing Algorithms for Next Generation System-in-Package

豊永 昌彦 1) 来栖 正博 2) ウプルヘラス 2) Masahiko Toyonaga 1) Masahiro Kurusu 2) Upul Herath 2) 1)高知大学 情報講座 2) 高知大学大学院理学専攻 Information Science Division, Faculty of Science, Kochi University

#### 概要

次世代SiP(システムインパッケージ)設計で求められる, 層数の制約と電気的ノイズの制約が可能な配線手法について3つの検討を行った.

まず、配線層数の最小が期待できる一層優先配線 アルゴリズムの構築と実装をおこない、SiP配線問題 で評価した。その結果、配線密度が高い場合には極 端に配線率が低くなることが判明した。

そこで、次に同配線法を経路検索自由度が2倍となる45度一層優先多層配線のアルゴリズムと実装による実験をおこなった。その結果、高い配線密度となるCSPにおいても高い配線率となることがわかった。また、その配線形状が人手設計並みであることがわかった。さらに、電気的ノイズ回避の制約についてクロストーク回避配線[C1]を45度一層優先多層配線へ適用する方法も検討し、それが可能であることがわかった。以上の研究から、次世代パッケージ配線自動化のアルゴリズムとして、45度一層優先多層配線が有力であることがわかった。

キーワード:パッケージ, SiP, 自動配線, ノイズ回避

#### 1. はじめに

半導体製造技術の微細化に伴い,電子回路システムを1チップで実現するS o C (システムオンチップ)による開発方法が提案されている. 一方,このような巨大化したL S I の製造歩留まり劣化や製造コスト増大に対して,1 チップ上ではなく複数のチップをパッケージ上で集積するS i P (システムインパッケージ)技術が注目されている.

S i Pとは多層配線可能なパッケージを用いて 複数のチップを搭載し、これら相互やパッケージ端 子までを配線する実装方式である.

一方,パッケージ製造技術が多種多様で,VLSIに比べて配線層数の制約や電気的ノイズの制約など配線形状に対して多くの制約がある.そのためVLSIのような自動配線手法が使えず,配線設計が人手中心に行われてきた.

しかし次世代SiPにおいて, さらなる機能向上が求められ搭載チップ数が増加すると, パッケージ配線の自動化技術は不可欠となる.

そこで著者は、本論文において次世代SiPの自

動配線技術について調査研究をおこなう.本論文では、SiP配線設計で求められる配線層数最小で、電気的ノイズ回避可能な自動配線手法について、新たな配線モデルと我々が提案するLSI配線設計のクロストーク回避配線技術によりその可能性を探る.

本論文では、次世代SiP配線自動化技術における高密度配線技術について2つの配線手法の検討と1つの考察を行う.

まず第1に検討した配線手法は、一層配線を優先的に利用する多層配線法である. SiP配線設計において、できるだけ一配線層内で配線を完了させることを目指すことで配線層数を少なくして製造コストが削減できる.

同配線手法では、一層配線を優先するため、従来の二層(縦横:HV)配線構造をとらない. もともとHV配線構造は、配線率を高めるために採用されてきた構造である. そのため、一層優先配線では配線率が低下することが懸念される.

そこで、本研究では実際に一層優先的多層配線アルゴリズムを構築してプログラム実装し、2つのSiP配線問題、MCM(Multi-Chip Module)およびBGA(Ball-Grid Array)に適用して配線率検証をおこなった。実験によれば、MCM配線問題で、十分な配線率が得られたものの、BGA配線問題では、配線率が低い結果となった。次世代パッケージ配線手法として、より高い配線率を得るためにはさらに工夫が必要である。

そこで第2の配線手法として,一層優先配線手法の検索自由度を2倍にする45度配線(同一配線層8方向検索)を導入する. 前述の一層優先配線法に比べて自由度を2倍高められるため配線率向上が期待できるためである.

先ほどと同様に、45度一層優先多層配線アルゴリズムを構築し、プログラム実装により先ほどのMCM配線問題やBGA配線問題で配線率の検証をおこなった.実験によれば、MCM配線問題では人手並みの形状と高密度の配線結果が得られた.またBGA配線問題でも高い配線率の結果が得られた.

以上の実験から次世代パッケージ配線自動化に おける配線層数の問題と配線率の問題については, 45度一層優先多層配線法で解決できそうであが, 「電気的ノイズ回避の制約」についての検討が残される. 配線層数削減は, 配線層間の接続(ヴィア)数を減らすため,ヴィアに起因する電気的ノイズ削減が期待できるものの,配線間のノイズは制御できない.

そこで著者は、VLSI自動配線設計で提案した クロストーク回避配線を第2の配線手法に拡張す ることの意義について検討をおこなった.

その結果、クロストーク回避配線法が45度一層優先多層配線法でも有効であり、これを実装することで次世代SiP配線自動化が可能性であることがわかった。

以下,第2章でSiPの概要について説明し,その自動化について従来手法の説明と本研究の位置づけをおこなう.第3章は,一層優先多層配線法についての説明とSiP配線問題における評価実験について述べる.第4章は,45度一層優先多層配線の説明とSiP配線問題における評価実験について述べる.第5章は,クロストーク回避配線について、FiP配線での拡張性と有用性について述べる.第6章で本研究をまとめ,続いて謝辞を述べる.

# 2. システムインパッケージ技術の概要

# 2.1. パッケージの概要

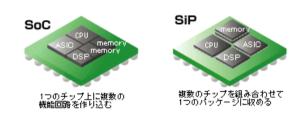

高機能化する近年の電子機器のコア部品の実現方法として、システムレベルを1 チップ上で実現するSoC(システムオンチップ)方式と、SoCと同等な機能を複数のチップを搭載するパッケージ、すなわちSiP(システムインパッケージ)方式に大別できる。図 2.1 にSoCおよびSiPのそれぞれの概念図を示す。

SoC方式の特徴は、システムを制御するCPU、信号処理用DSP、データやパラメータを記憶するメモリなどで構成される巨大なLSIである.サイズが巨大となるため設計に要する時間やコストは膨大で、また、製造に際しても高い歩留まりとすることが難しい。SoCでは、設計期間の短縮やコストの削減、さらに製造時の歩留まり改善などの問題が課題となる.

一方、SiP方式は、既に製造済みの複数チップを組み合わせて作るため、設計がパッケージ上の配置と配線設計のみであり、短期でかつ低コストとなる。また、SoCで混載した製造が難しいアナログ回路やメモリ回路をそれぞれ独立して製造後に混載できる点もSiPの利点である。

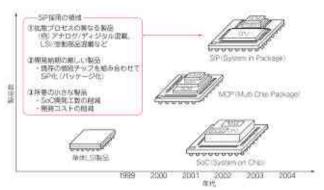

近年では、機器の小型化に伴い、SiPの小型化も進められている。図2.1.2 は、SoCとSiPのトレンドの概要を示したもので、チップ部品を平面だけではなく、重ねる実装(3D実装)で小型されていることがわかる[1].

現在はまだ搭載されるチップ数が少なく、またSiP加工技術が様々提案されている段階であるため、SiP技術の主流はパッケージ基板(インタポーザ)の多層加工技術や部品実装技術が中心となっており、SiP設計のほとんどは配線も含めて人手で行われている。

図 2.1.1 SoCとSiP(NECエレクトロニクスサイト)

図 2.1.2 SoCとSiPのトレンド[1]

### 2.2. SiPの種類

I CやLS I など半導体部品の強度を保ち, 防湿により品質を保つために, 従来からも樹脂やセラミックなどのパッケージが必要とされてきた.

このような半導体チップ用のパッケージの役割は、ベアチップ(シリコンそのままの状態のIC)の入出力(IO)端子とパッケージ端子(リード)をボンディングワイヤで機械的に接続することで、パッケージの端子を通じてICを動作させるためであった.

多くの回路基板は、プリント基板上にこれらパッケージされた I Cを搭載して構成されている.

個別 I Cのパッケージ方式は, 主に端子配列により区別される. 代表例を次に示す.

#### 1) DIP (Dual Inline Package)

長方形に加工されたセラミックあるいはプラスチックの小片の側面に端子(リード)が並んだ形状をとる.チップとリードとはボンディングワイヤで機械的に接続する. TTLICのような標準デジタ

ルICで多く見られる.

# 2) PGA (Pin Grid Array)

ほぼ正方形に加工されたセラミックあるいはプラスチックの小片の底面に端子(リード)が針のようにして並んだ形状をとる.チップを反転してリードとは半田ボールを介して接続させて配線する(FlipChip). CPUなど多端子をもつICで多く見られる.

#### 3) QFP (Quad Flat Package)

ほぼ正方形に加工されたプラスチックの小片の周囲に端子(リード)が並んだ形状をとる.小型CPUやメモリなどで多く見られる.高密度実装において用いられる.

#### 4) BGA (Ball Grid Array)

ほぼ正方形に加工されたプラスチックの小片の 底辺に端子(リード)相当の半田ボールが並んだ形 状をとる.チップを反転してインターポーザを介し てチップ I Oと多層配線で端子まで配線する(Flip Chip).特に高密度実装において用いられる.

#### 5) CSP (Chip-Size Package)

パッケージされた個別ICとして最小サイズとなるパッケージで、チップIOとチップが搭載されたインタポーザの裏面のBGA端子までの配線さされる、最も高密度実装となる。

SiРのように複数チップを搭載するパッケージ基板は、個別ICのパッケージの搭載と、ベアチップを搭載したもので区別され、代表例は次のとおりである.

# 1) MCM (Multi-Chip Module)

複数のベアチップを1つのパッケージに実装して,主にボンディングワイヤーでチップや端子を配線したものを指す.チップは主に2次元的に配置されている.

# 2) MCP (Multi-Chip Package)

複数のベアチップを1つのパッケージに実装して,ボンディングワイヤーやパッケージ内配線でチップや端子を配線しているが,チップが3次元的に配置されることもある.

#### 2.3. パッケージの自動設計技術

現在はまだ搭載されるチップ数が少なく,またSiP加工技術が様々提案されている段階であるため,SiP技術の主流はパッケージ基板(インタポーザ)の多層加工技術や部品実装技術が中心となっており[2][3],SiP設計のほとんどが配線も含めて人手で行われている.

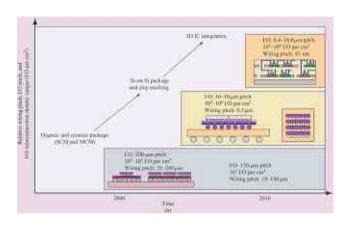

しかし,図 2.3.1 に示すように次世代SiPにおいてチップ数が増え,チップ性能が向上した場合には,加工技術だけではなく,次のような設計問題,すなわち

- 1) コスト削減のための配線層数最適化

- 2) 性能保証のための電気的ノイズ対策[4][5]

- 3) 搭載する個別チップの小型化設計技術[6] などである.

これら多数の制約をもつ次世代SiP設計を人手で設計することは難しい.

次世代のSiPでは、さらに多数のチップ実装にともない膨大な配線設計が必要となるため[7]、その配線自動化技術の確立が求められる.

図 2.1.3 次世代 S i Pのトレンド[7]

従来提案されているパッケージ配線技術として、久保、高橋[8]は、BGA(Ball Grid Array)パッケージの一層配線法を提案しており、配線層と端子ボールが共存する配線層において配線長、配線混雑度を考慮して概略経路を自動生成してから配線経路を決定する方法について述べている。また[9]において、一層配線では端子配列を逆行配列で修正して配線密度が削減できる方法を提案している。

R.Wang 等[10]は、BGA 方式の CSP パッケージに ついてネットワークフローモデルを用いて配線通 過数のボトルネックを分析して必要配線層数を数 学的手法でモデル化した.

従来手法は、パッケージ配線モデルがVLSI配線モデルと異なることから、一層のみ、あるいは、指定した層のみを使う新たな配線法を提案している.一方、これらは次世代SiPのように複雑で制約の多い配線として使用できる保証はない.一方、モデルは異なるが、VLSI配線法は既に数十年の利用経験を持ち、配線率向上などで多くの実績を持つ

我々は、これら実績を持つVLSI配線法を中心

に次章以降でSiP求められる配線層数最適化,電気的ノイズ対策,搭載する個別チップの小型化設計技術について検討していく.

## 3. 一層優先多層配線法

# 3.1. 多層配線モデル

本論文で提案する配線法は、迷路配線法に基づいている。そこで、まず迷路配線法で用いられる配線 モデルについて以下で説明する。

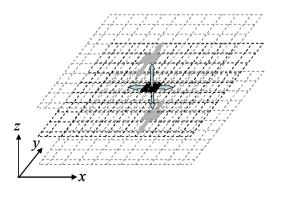

迷路配線では、配線領域に碁盤の目のような格子 (グリッド)を設定し、これを配線モデルとして利用する.ここでグリッドの間隔は、配線デザインルールに基づいた層間接続 (ヴィア) や配線が隣接可能な最短距離を1とする.

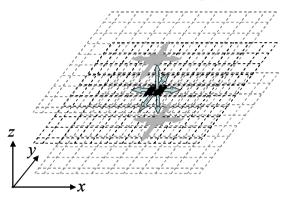

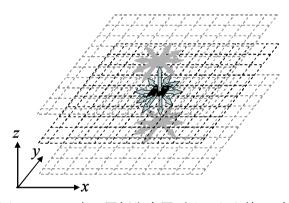

配線探索時に最隣接グリッド間を結線さえすれば、配線デザインルールの遵守が保証され、また、グリッド距離がそのまま配線距離として評価することができる.多層配線問題では、層間を垂直方向(z軸)、層内を縦(y軸)、横(x軸)としたグリッド配線モデルが用いられる.(図 3.1)

従来の配線法では、配線率を高める経験則からグリッド配線モデルとして路探索方向を各層でx方向とy方向に限定したHV(Horizontal-Vertical) 配線方式が用いられる. 図 3.1 の例では、偶数番目の層はx(横)方向中心、奇数はy(縦)方向中心に配線検索をおこなうという具合である. 従って、H V配線方式では、図 3.2 のように水平垂直で異なる層を用いた配線結果となる.

本論文で提案する一層優先多層配線法では, S i Pに要求される「配線層数の制約」の点から, より少ない層数で配線するためにHV配線方式をやめて, 層間の移動1グリッド分の距離に相当するため, 同一配線層状の経路が優先的に検索されることになる.

図 3.1.1 多層グリッド配線モデル

図 3.1.2 HV 配線方式による多層配線結果

図 3.1.3 一層優先多層グリッド配線モデル

# 3.2. 一層優先多層配線アルゴリズム

提案する一層優先配線法は、多層迷路配線法と同じであるが、検索方向についてより多くの自由度を持っている.

迷路配線法は,グリッド配線モデル上に定義された始点と終点について,最短かつ経路があれば必ず見つけ出すアルゴリズムである.迷路配線アルゴリズムを図3.2に示す.

#### 一層優先多層迷路配線アルゴリズム

- 0°始点を検索点リストへ登録し、次検索候補点リストを空にする.

- 1°検索リストの全点に対して隣接する縦横上下グリッドを調べて以下の判定を行う

- 1.1 もし隣接グリッドが終点ならトレースバック処理をおこなってステップ 3°へ

- 1.2 もし隣接グリッドが障害物でないなら次検索候補点リストへ登録する

- 1.3 もし隣接グリッドが障害物ならなにもしない.

- 2°次検索点リストの全点に対して以下の処理をおこなう.

- 2.1 もし次検索候補点リストが空ならば、「経路なし」と判定して5へ

- 2.2 検索点リストを次検索候補点リストで置き換えて、次検索候補点 リストを空にし、ステップ 1°へ

- 3°結果を出力して終了する

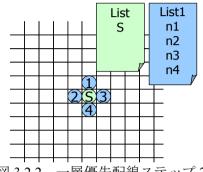

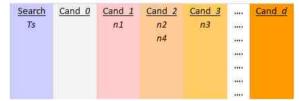

迷路配線法では、「検索点リスト」と「次検索候補点リスト」という2種類のリストを用いる.アルゴリズムの準備として、まず始点を検索点リストに登録する.

図 3.2.1 一層優先配線ステップ 1°

図 3.2.2 一層優先配線ステップ 2°

経路探索では「検索点リスト」から検索点を取り 出し、その隣接グリッド格子を調べ、同検索点から 隣接グリッド間を結線できるならば次検索候補リ ストに登録する.検索点リストをすべて処理したな らば, 次検索候補リストを検索点リストとして再び 繰り返す.途中で終点を発見したならば,処理を終 了し、終点から経路を逆にたどって(トレースバッ クして)経路を確定する.

図 3.2.1 に、Sを始点として検索点リスト、次検 索候補リストを示す. また, 図 3.2.2 に, Sの隣接 グリッドの状態を調べ、配線可能なグリッド nl~ n4 を次検索候補リストに登録したようすを示す.

#### 3.3. 一層優先多層配線のSiP配線実験

提案する一層優先多層配線アルゴリズムをプロ グラム実装し、簡単なSiP配線問題として MCM(マルチチップモジュール)と BGA (ボールグ リッドアレイパッケージ)に適用して従来のHV配 線法と比較する実験をおこなった. プログラム言語 は Cvgwin-GCC コンパイラを用いた.

#### 3.3.1. MCM における配線結果の比較

MCMの配線結果を,図3.3.1aと図3.3.2bに示す. 図において、中央に2つのチップ領域がみられる. 図 3.3.1a と図 3.3.2b を比べると, 一層優先配線 では, 二層(緑色), 三層(青色)配線が少なく, 一層(紫色)で多くの配線が完結していることが わかる.

図 3.3.1a HV配線方式による配線結果

図 3.3.1b 一層優先配線方式の配線結果

# 3.3.2. BGA における配線結果の比較

BGA の配線結果を,図3.3.2a と図3.3.2b に示す. 端子は2次元上に分布しており,配線数も先ほどの MCM に比べて多い、そのため、どちらの場合も未 配線が生じた. HV 方式では、全324 ネットの配線 において 92/324 の配線率、提案手法では、103/324 の配線率であった.

図 3.3.1a HV配線方式による配線結果

図 3.3.1b 一層優先配線方式の配線結果

#### 4. 45度一層優先多層配線法

前章の結果から、一層優先多層配線そのままでは SiPにおける「配線層数の制約」を保つことはできるが、配線率が極端に低くなる場合があることが わかった.

そこで本章において第2の配線手法として一層優先多層配線に比べて経路検索の自由度を2倍に増やした45度(同一層内8方向)一層優先多層配線手法について述べる.ここで提案する45度一層優先多層配線法は,従来の迷路配線法を各配線層で縦,横,45度の8方向の経路検索可能となるよう拡張したものである.

45 度一層優先多層グリッド配線モデルを図 4.1.1 に示す. 層間の検索方向も含めれば 10 方向の経路 検索をすることがわかる.

図 3.1.3 45 度一層優先多層グリッド配線モデル

# 4.1. 45 度一層優先多層配線アルゴリズム

45 度一層優先配線法もまた,グリッド配線モデル上に定義された始点と終点について,最短かつ経路があれば必ず見つけ出すアルゴリズムである.迷路配線アルゴリズムを図 4.1 に示す.

# 45 度一層優先多層迷路配線アルゴリズム

- 0°始点を検索点リストへ登録し、次検索候補点リストを空にする。

- 1°検索リストの全点に対して隣接する縦横上下および 45 度方向のグリッドを調べて以下の判定を行う

- 1.1 もし隣接グリッドが終点ならトレースバック処理をおこなってステップ 3°へ

- 1.2 もし隣接グリッドが障害物でないなら次検索候補点リストへ登録する

- 1.3 もし隣接グリッドが障害物ならなにもしない.

- 2°次検索点リストの全点に対して以下の処理をおこなう.

- 2.1 もし次検索候補点リストが空ならば、「経路なし」と判定して5へ

- 2.2 検索点リストを次検索候補点リストで置き換えて、次検索候補点 リストを空にし、ステップ 1°へ

- 3°結果を出力して終了する

#### 4.2. 一層優先多層配線のSiP配線実験

提案する 45 度一層優先多層配線アルゴリズムを プログラム実装し、先ほどと同様に簡単なSiP配 線問題として MCM(マルチチップモジュール)と BGA (ボールグリッドアレイパッケージ) に適用 して従来のHV配線法と比較する実験をおこなっ た. プログラム言語は Cygwin-GCC コンパイラを 用いた.

#### 4.2.1. MCM における配線結果の比較

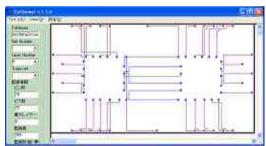

MCMの配線結果を,図4.2.1aと図4.2.1bに示す. なお、図4.2.1aは、図3.3.1bと同じ図である.

図 4.2.1a 一層優先配線方式の配線結果

図 4.2.1b 45 度一層優先配線方式の配線

図 4.2.1c 人手による配線結果

図 4.2.1a と図 4.2.2b を比べると, 45 度の自由 度一層優先配線では,より配線長が短い配線となることがわかる. また,図 4.2.2c に示した人手設計に比べても近い形状が得られていることがわかる.

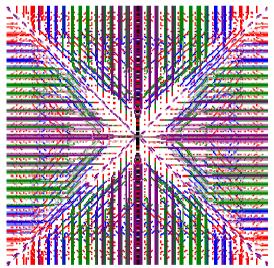

### 4.2.2. CSP における配線結果の比較

CSP(fップスケールパッケージ)の配線結果を、図 4.2.2a と図 4.2.2b に示す. CSP では、端子は 2 次元上に分布しておりこれらを外周上まで配線する.問題である. 配線順序を調整することでグリッドサイズ  $120 \times 120$ , ボール端子数 253, 端子ピッチ 4, 配線層は 4 において、配線率 253/253 (完全配線) が得られた.

図 4.2.2a 一層優先配線方式の配線結果

図 4.2.2a 一層優先配線方式の配線結果

#### 4.2.3. 提案手法のSiP自動配線の可能性

以上の計算機実験から、45 度一層優先多層配線 法は、MCM、CSP などの配線問題で「配線層数の 制約」について実用的なレベルの高い配線率が得ら れることがわかった。

今後、BGA などさらに高密度配線問題に適用した評価をおこなう予定である.一方、SiP自動配線における「電気的ノイズの制約」を実現する配線手法が残されている.

#### 5. ノイズ制御への展望

本章では、SiP自動配線における電気的ノイズ

の制約について,クロストーク回避配線の展開による解決方法について検討する.

#### 5.1.1. クロストーク回避配線法

著者らは、すでに 45 度一層クロストーク回避配線手法(ORCA)を確立している[11][12]. クロストーク回避問題とは、指定する配線間の距離を指定以上はなして配線する経路を探索する問題である.

ー層クロストーク回避配線アルゴリズムを図 5.1. 1 に示す.

```

Algorithm ORCA

Input: obstacles, aggressor (w_2), start point (Ts) and end

point (Te) of victim (w_1), and specified crosstalk avoidance

distance (d)

Output: Crosstalk-avoiding octalinear route of w_1

OR CA {

input()

for (w_1, w_2) {

set obstacles, w2, Ts, Te, and routable area label (0);

set distance labels around w_2 with thickness d;

assign Ts to search-list;

for each point p in search-list {

for each eight neighboring point p_n {

if p_n is Te then go to trace-back();

else if p_n is labeled j (0 < j < d), then assign p_n to

list-j;

lookup points in lists-j in ascending order of j, and

move routable points to search-list from list-j with

least i so found:

clear list-j;

if there is no list-j with routable points for all j, then

stop with error message;

trace-back();

output();

```

図 5. 1.1 45 度クロストーク回避アルゴリズム ORCA

ORCAでは、迷路配線法と異なり、「検索点リスト」とn個の「次検索候補点リスト I (i=1,2,..n)」を用いる.アルゴリズムの準備として、まず始点を検索点リストに登録し、さらにグリッド配線上に回避ラベルを付与する.

経路探索では「検索点リスト」から検索点を取り出し、その隣接グリッド格子を調べ、同検索点から隣接グリッド間を結線できるならば次検索候補リストに登録する.このとき、回避ラベル番号に応応で、次検索候補点リスト番号を振り分ける.検索にリストすべて処理したならば、空でない次検索候補リストiのうちiが小さいリストを検索点リストはして再び繰り返す点で異なる.途中で終点を発見したならば、処理を終了し、終点から経路を逆にたどって(トレースバックして)経路を確定する点は迷路配線法と同じである.

図 3.2.1 に、Sを始点として検索点リスト、次検索候補リストを示す. また、図 3.2.2 に、Sの隣接グリッドの状態を調べ、配線可能なグリッド n1~

n4 を次検索候補リストに登録したようすを示す.

| 0 | 0 | 0 | 0  | 0              | 0   | 0 | 0 | 0 | 0 | 0  | 0 |

|---|---|---|----|----------------|-----|---|---|---|---|----|---|

| 0 | 0 | 0 | 0  | 0              | 0   | 0 | 0 | 0 | 0 | 0  | 0 |

| 1 | 1 | 1 | 1  | $\overline{a}$ | 1   | 1 | 1 | 1 | 1 | 1  | 1 |

| 2 | 2 | 2 | 64 | TS             | (2) | 2 | 2 | 2 | 2 | Te | 2 |

| 3 | 3 | 3 | 3  | r3             | 3   | 3 | 3 | 3 | 3 | 3  | 3 |

| 8 |   | 3 | *  | 2              | *   | 8 | : | 3 | * | 8  | : |

| d | d | d | d  | d              | d   | d | d | d | d | d  | € |

| d | d | d | d  | d              | d   | d | d | d | d | d  | € |

| è | 1 | 3 | *  | 2              | 1   | è | : | è | 1 | 3  | 1 |

| 3 | 3 | 3 | 3  | 3              | 3   | 3 | 3 | 3 | 3 | 3  | 3 |

| 2 | 2 | 2 | 2  | 2              | 2   | 2 | 2 | 2 | 2 | 2  | 2 |

| 1 | 1 | 1 | 1  | 1              | 1   | 1 | 1 | 1 | 1 | 1  | 1 |

| 0 | 0 | 0 | 0  | 0              | 0   | 0 | 0 | 0 | 0 | 0  | C |

| 0 | 0 | 0 | 0  | 0              | 0   | 0 | 0 | 0 | 0 | 0  | 0 |

図 5.1.2 ORCA 隣接候補点を複数の次検索候補 リスト 0~d へ振り分ける様子

提案する 45 度一層優先多層配線アルゴリズムをプログラム実装し、先ほどと同様に簡単なSiP配線問題として MCM(マルチチップモジュール)とBGA (ボールグリッドアレイパッケージ) に適用して従来のHV配線法と比較する実験をおこなった. プログラム言語は Cygwin-GCC コンパイラを用いた.

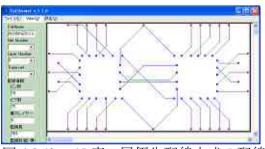

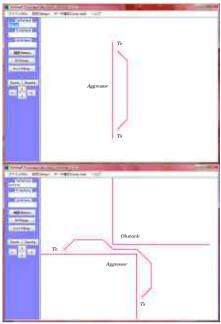

図 5.1.3a 従来配線による配線結果

図 5.1.3b ORCA による配線結果

図 5.1.2a と図 5.1.2b を比べると, ORCA が指定した距離 d の距離を離して 45 度配線をおこなっていることがわかる.

#### 5.1.2. ORCAのSiP自動配線の適用可能性

事前のラベル付け処理を除くと、ORCA を 45 度 一層優先配線アルゴリズムに組み込むことは容易である。また、ORCA は、ラベル付けを変えることで様々な配線間の回避経路を検索する可能性をもっている。

今後, Si Pがさらに高密度化や電気的ノイズ問題解決のために複雑化した制約をもつ場合でも,対応できるものと思われる.

## 6. まとめ

本論文で次世代パッケージ配線に求められる,層数の制約と電気的ノイズの制約が可能な配線手法について検討を行った.

まず、HV構造をやめて同一層内で縦横を自由に利用する一層優先配線法について研究をおこない、SiP配線問題におけるMCMにおいて同配線手法によりヴィア数削減ができることが明らかになった.一方、配線密度が高いCSPでは配線率が極端に低くなることも判明した.

そこで,次に同配線法を経路検索自由度を2倍に した45度一層優先多層配線へ拡張する研究をお こなった.前述の一層優先多層配線法に比べてCS Pにおいて高い配線率が得られ,またMCMにおい ても人手設計と類似する配線が得られることがわ かった.

以上の研究で残された電気的ノイズ回避の制約 についてクロストーク回避配線[12]の展開可能性 についても検討し、それが可能であることがわかっ た.

以上の研究を通じて,これらの配線手法を組合わせることで次世代パッケージ配線自動化の可能性があることがわかった.

#### 铅憔

著者は,本研究への助成いただいた,財団法人 高 橋産業経済研究財団(平成 21 年度助成)に深く感 謝いたします.

また, S i P配線モデルについて有用な議論をいただいた株式会社ケイレックスの川瀬英路様に深く感謝いたします.

### 参考文献

- [1] 中島宏文「最新半導体パッケージの基礎知識」 トランジスタ技術 2004 年 7 月.

- [2]阪本,杉田,菊池,田中,赤沢「RenesasSiP のシステム実装技術課題とその解決法」電子情報通信学会技術報告 ICD2005-100,pp.31-34(2005)

- [3]嶋田勇三「先端実装技術の動向と今後の展望」 電子情報通信学会論文誌 C,Vol.J88-C, No.11, pp.827-838 (2005)

- [4]益子行雄「デバイスの高速化に対応した設計技術」エレクトロニクス実装学会誌,Vol.4,No.3,pp176-180(2001)

- [5]小澤,合葉,平岡,小酒井,高島「SiPの電気特性評価」エレクトロニクス実装学会誌,Vol.6,No.4,pp326-331(2003)

- [6]西山和夫「デジタル家電の実装ニーズと半導体パッケージング技術」エレクトロニクス実装学会誌,Vol.4,No.3, pp166-169(2001)

- [7] Three Ddimensional Silicon Integration,"IBM Journal of Research & Development, Vol52, No.6, pp553-569(2008)

- [8] 久保ゆき子,高橋篤司"2 層 BGA パッケージ配線の概略経路自動生成"pp. 535-540,第17回 回路とシステム軽井沢ワークショップ 2004 年4月26,27日

- [9]野村義孝,高橋篤"BGA パッケージにおける最大密度 を低減する順行配列修正法の提案"(2006 年)

- [10] Renshen Wang ,Rui Shi, Chung-Kuan Cheng, "Layer Minimization of Escape Routing in Area Array Packaging," ICCAD'06, November 5-9, 2006.

- [11] 竹谷 啓, 張 汎, 豊永昌彦 クロストーク回避 迷路配線の一手法 1-3 平成 19 年度電気関係学会

四国支部連合大会 1-3 (2007 年 9 月 29 日徳島大) [12]Upul Herath, Michiaki Muraoka, Masahiko Toyonaga ORCA: An Octalinear Router for Crosstalk Avoidance 17-46 平成 20 年度電気関係学会 四国支 部連合大会 17-46 (2008 年 9 月 27 日徳島大)