# FPGA を用いた論理シミュレーション手法の研究

A Logic Simulation Method using FPGA

松本 夏樹 村岡 道明

高知大学大学院 理学専攻 情報科学分野

#### 1. はじめに

大規模回路やシステムの論理検証には,ソフトウェアとハードウェアの協調シミュレーションが行われており,大規模なハードウェアのシミュレーションには FPGA を用いた論理エミュレータが使用されているが,FPGA の再構成に膨大な時間がかかりデバッグ性が良くない.本研究では,先行研究[1]を基にレベルソート法を用いたデバッグ性の高い論理シミュレーションのハードウェアアルゴリズムの提案,及び本アルゴリズムを FPGA に実装しシミュレーションエンジンの試作を行った.

## 2. ハードウェアアーキテクチャ

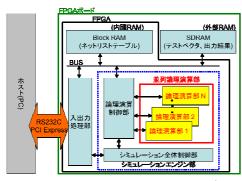

提案するシミュレーションエンジンのハードウェアア ーキテクチャの概要を図1に示す.

図1 ハードウェアアーキテクチャの概要

まずホストから送信されるシミュレーション対象回路のネットリストテーブルやテストベクタを入力処理部で受信し、ネットリストテーブルは FPGA 内臓RAM(BRAM)、テストベクタは外部 RAM(SDRAM)に格納する、次に論理演算制御部で演算を行う論理ゲートのネットリストテーブルを読込み、論理演算部で論理演算を行う。最後に出力処理部でシミュレーション結果をホストへ送信する、シミュレーション全体制御部では、シミュレーション全体の制御を行う、論理ゲートの論理演算を行う論理演算部を並列数用意することで、論理ゲートの並列演算を実現し高速化を図る、ホストと FPGA の通信は RS232C や PCI Express を用いる.

### 3. 実装対象とする FPGA

本研究で実装対象とする FPGA の詳細を以下に示す.

FPGA: ALTERA Cyclone III 3C16

-LE(ロジックエレメント)数 : 15,408 個

-M9K メモリブロック(BRAM): 56 個

対象とする FPGA の場合,シミュレーション可能最大 ゲート数は4,096で,論理ゲートの演算を行う論理演算部 は16並列まで可能である.また,本研究ではシミュレーションエンジンの性能評価のための試作として,安価なFPGAを使用したが,大規模高性能FPGAへの展開も可能であり,更に並列数を増やすことができる.

#### 4. 評価

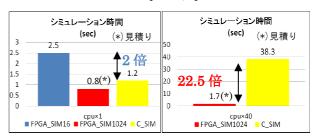

提案するハードウェアアルゴリズムを対象とする FPGA 〜実装した場合の並列数 16 のシミュレーション エンジン(FPGA\_SIM16)のシミュレーション時間と商用 高速論理シミュレータ  $C_SIM$  のシミュレーション時間 を比較した結果  $(cpu \times 1)$  を図 2 に示す.また,並列数 1,024 の場合(FPGA\_SIM1024)のシミュレーション時間  $(cpu \times 40)$  を実測の周波数に基き見積り, $C_SIM$  と比較をした結果を図3に示す.見積りは1 サイクルにかかる処理クロック数×テストベクタ長÷周波数で求めた.

<動作環境・実験条件>

· C SIM: ModelSim SE 10.2c

テストベクタ長:100,000 サイクル

・FPGA 動作周波数:100MHz

• 実験回路: 順序回路 cpu×1, cpu×40

図 2.FPGA\_SIM の比較結果

図 3. 並列数 1024 の場合の比較結果

## 5. 結論・今後の課題

本研究では、FPGA を用いたシミュレーションエンジンの試作を行った.商用高速論理シミュレータと比較して、並列演算数 16 のシミュレーションエンジンは順序回路  $cpu \times 1$ (約 2,000 ゲート)で約 2 倍遅い結果となったが、並列数 1,024 では高速化される.並列演算数 1,024 の場合を見積ると,順序回路  $cpu \times 40$ (約 8 万ゲート)で約 22.5 倍の高速性が達成できる見通しを得られた.

今後の課題としては、大規模回路対応や FPGA を用いた論理エミュレータとの総合的な比較、更なる高速化が考えられる。論理ゲートの複合化や LSI 化等により  $C_SIM$  と比較して 2,200 倍以上の高速化も期待できる.

### 参考文献

[1] 松本夏樹, 村岡道明, "FPGA を用いた論理シミュレーション手法", デザインガイア 2013, 2013 年 11 月